硬件产品开发总结(二) 硬件开发的流程、挑战与最佳实践

在硬件产品开发的宏大蓝图中,硬件开发是承上启下的核心阶段。它将前期的概念设计、需求分析与架构规划,转化为实实在在、可测试、可生产的物理实体。本部分将系统性地硬件开发的关键流程、常见挑战与应对策略,为开发者提供清晰的实践指引。

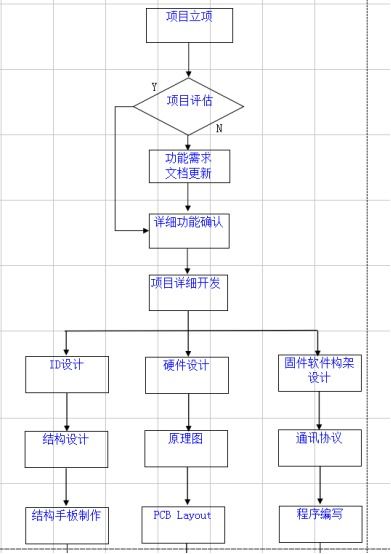

一、硬件开发的核心流程

硬件开发并非简单的“画板子、做样品”,而是一个严谨的、多迭代的工程过程。其典型流程可分为以下几个阶段:

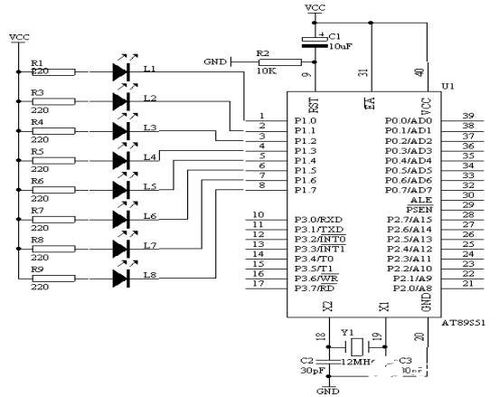

- 详细设计与元器件选型:基于产品规格书(PRD)和系统架构,进行详细的原理图设计。此阶段的核心挑战在于元器件选型——需要在性能、成本、功耗、供货周期、可靠性及可获得性(如车规级、工业级)之间取得最佳平衡。建立并维护一个经过验证的“优选元器件库”至关重要。

- PCB设计与仿真:将原理图转化为PCB布局。这不仅是连线的艺术,更是电磁兼容(EMC)、信号完整性(SI)、电源完整性(PI)和热管理的综合博弈。关键工作包括:层叠设计、高速信号线(如DDR, PCIe)的拓扑与等长处理、电源分割、去耦电容的优化布局、以及地平面的完整性。前期利用仿真工具(如SI/PI仿真)预测问题,能大幅减少后期调试的试错成本。

- 原型(EVT)制作与调试:发出首版(V1.0)PCB进行打样与贴片,组装成工程原型机。调试阶段是发现问题、验证设计的开始。开发者需要系统地进行电源上电时序与纹波测试、时钟与复位信号质量测试、关键接口(如USB, Ethernet)功能测试,并使用示波器、逻辑分析仪等工具定位故障。详细的调试记录是宝贵的知识资产。

- 设计验证测试(DVT)与可靠性验证:在原型功能基本正常后,进入严格的DVT阶段。此阶段目标在于全面验证产品是否符合所有设计规格与行业标准。测试内容包括但不限于:环境应力测试(高低温、湿度)、机械应力测试(振动、跌落)、长时间老化测试、EMC预兼容测试、安规测试以及完整的系统功能与性能测试。任何在此阶段发现的问题都必须回溯到设计端进行根因分析并修改。

- 设计固化与转产准备(PVT):当设计通过DVT验证后,进入小批量试产阶段。此阶段的目标是验证制造流程、夹具、测试方案及供应链的稳定性,确保产品能以一致的良率大规模生产。需要输出全套的生产制造文件(Gerber, BOM, 装配图,测试程序等)并完成对工厂的技术交底。

二、硬件开发中的主要挑战与应对

- 跨领域协同复杂:现代硬件产品是软硬件的高度集成。硬件开发者必须与结构、软件、射频、测试、供应链团队紧密协作。建立清晰的接口文档(如引脚定义、通信协议)、定期的协同会议以及使用协同管理工具(如Jira, Confluence)是保障项目顺畅的关键。

- 信号与电源完整性挑战:随着处理器速度提升和供电电压降低,SI/PI问题日益突出。最佳实践包括:在布局前制定详细的布线约束规则;对关键网络进行仿真;采用多层板并为关键电源与地提供完整平面;在电源入口和芯片电源引脚附近合理布置不同容值的去耦电容。

- 热设计与管理:功耗带来发热,过热导致性能下降乃至损坏。需从系统层面考虑散热:合理布局高热器件、使用热仿真优化散热路径、选择有效的散热方案(如散热片、风扇、热管)、并在结构设计上预留风道。

- 可测试性设计(DFT)与可生产性设计(DFM):为后期测试和生产便利,应在设计初期就融入DFT/DFM思想。例如,添加关键的测试点、JTAG接口;考虑PCB的工艺边、拼板方式、元器件的封装是否便于自动化贴装等。与制造厂的早期沟通能有效避免此类问题。

- 变更管理与成本控制:开发过程中的设计变更是常态,但必须被严格管理。任何变更都应评估其对成本、 schedule和已生产物料的影响。使用版本控制工具管理原理图与PCB文件,并确保BOM的每一次变更都有据可查。

三、给硬件开发者的建议

- 文档至上:从设计规范、评审记录到调试报告,详尽及时的文档是团队协作和知识传承的基石。

- 仿真先行:在资金和时间允许的情况下,尽可能在投板前进行仿真,将问题消灭在图纸阶段。

- 模块化与复用:将经过验证的电路模块(如电源、MCU最小系统)标准化、模块化,能显著提升后续项目的开发效率与可靠性。

- 拥抱调试:调试是硬件工程师的核心能力。保持耐心,遵循“由大到小、由电源到信号”的系统化排查思路,并善用仪器设备的进阶功能。

- 保持好奇心与持续学习:新技术、新器件、新工艺不断涌现。关注行业动态,理解底层原理,才能设计出更具竞争力的产品。

硬件开发是一场需要精密规划、严谨执行和持续优化的“持久战”。成功的硬件产品,其背后必然是一套融合了创新设计、工程严谨性与供应链智慧的完整开发体系。当硬件平台稳定可靠地搭建起来,它便为软件的精彩演绎提供了最坚实的舞台。

如若转载,请注明出处:http://www.didihaohuo.com/product/31.html

更新时间:2026-01-13 12:46:57