CPRI协议分析仪的硬件开发与软件实现

CPRI(通用公共无线电接口)协议是无线通信基站设备中连接无线设备控制单元(REC)和无线设备(RE)的关键内部接口标准。CPRI协议分析仪作为研发、测试和维护的核心工具,其开发涉及精密的硬件设计与复杂的软件实现。本文将系统阐述CPRI协议分析仪的硬件开发与软件开发过程。

一、 硬件开发

硬件是CPRI协议分析仪的物理基础,负责信号的接入、处理与初步解析,其设计直接决定了仪器的性能上限。

1. 总体架构设计

硬件系统通常采用模块化设计,核心模块包括:

- 高速接口模块:负责物理层信号的接入。核心是支持CPRI标准速率(如614.4 Mbps至24.33 Gbps)的高速串行收发器(SerDes),通常基于FPGA实现,并配备SFP+/QSFP+等光模块接口,以适配不同的光纤链路。

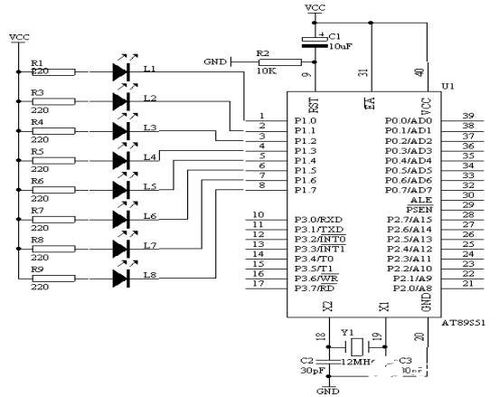

- 核心处理模块:以高性能FPGA(如Xilinx UltraScale+或Intel Stratix 10系列)为核心。FPGA负责实现CPRI协议的底层帧解析、时钟恢复、数据成帧与解帧,以及硬件时间戳等实时性要求高的处理任务。

- 数据缓存与交互模块:包含大容量、高带宽的DDR4内存,用于临时存储海量的IQ数据和控制面数据。通过PCIe总线与上位机进行高速数据交互。

- 时钟与同步模块:提供高精度、低抖动的时钟源,并支持从CPRI链路中恢复时钟(钟源恢复),或接受外部参考时钟输入,确保分析仪与被测系统的时间同步。

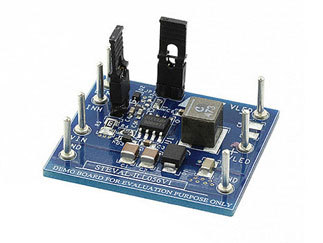

- 电源与辅助电路:为各模块提供稳定、洁净的电源,并设计必要的配置、状态指示灯等辅助电路。

2. 关键硬件技术

- 高速SerDes设计:这是硬件设计的难点。需精确控制信号完整性,通过仿真优化PCB布局布线,确保在高速率下的低误码率。

- FPGA逻辑设计:在FPGA内实现CPRI协议的状态机、解码器、流量控制器以及DMA引擎,要求设计兼顾高性能、低延迟和资源优化。

- 散热与结构设计:高速电路功耗大,需采用有效的散热方案(如散热片、风扇)和坚固的机械结构,保证设备长期稳定运行。

二、 软件开发

软件是CPRI协议分析仪的灵魂,它将硬件捕获的原始数据转化为用户可理解、可操作的信息,并提供友好的人机交互界面。

1. 软件架构

软件系统通常采用分层架构:

- 底层驱动与固件:运行在FPGA上的嵌入式固件(通过HDL或HLS开发),负责与硬件逻辑紧密交互,执行数据采集、预处理和传输指令。主机端的驱动程序(如基于Linux或Windows的PCIe驱动)管理硬件资源,为上层层提供API。

- 核心协议分析引擎:这是软件的核心。它接收来自硬件的原始数据流,完整解析CPRI协议栈,包括:

- 物理层:验证线路速率、编码和同步状态。

- 数据链路层:解析基本帧、超帧和无线帧结构,提取IQ数据、控制与管理面信息(C&M)、同步与定时信息、厂商特定信息等。

- 高层协议:进一步解码C&M通道中的HDLC/以太网封装以及上层协议(如IPC、LTE/5G层1控制信令等)。

- 数据存储与管理模块:支持将海量数据流实时存储到硬盘(如RAID阵列),并提供高效的检索和回放功能。

- 图形用户界面(GUI):提供直观的可视化界面,用于配置参数(如端口、速率、过滤条件)、实时监控链路状态(如误码率、告警)、多窗口显示IQ波形、协议消息解码列表、统计图表(如流量、延迟)等。

- 自动化与API:提供脚本接口(如Python API)和自动化测试套件,支持用户编写自定义测试流程,实现批量测试与集成。

2. 关键软件技术

- 实时流处理技术:面对Gbps级别的数据流,需采用高效的多线程、环形缓冲区和零拷贝技术,确保数据不丢失、处理低延迟。

- 协议解码库:构建可扩展、模块化的协议解码库,便于支持CPRI协议的不同版本以及其中封装的各类无线制式信令。

- 数据可视化:开发高性能的绘图组件,能够流畅渲染随时间变化的IQ信号和大量协议事件。

三、 硬件与软件的协同

CPRI协议分析仪的成功关键在于硬件与软件的深度协同优化:

- 任务分工:将时间敏感、计算密集的协议解析底层任务(如帧同步、解复用)固化在FPGA硬件中;将复杂的、灵活的上层解码、显示和用户交互交由软件处理。

- 接口定义:硬件与软件之间通过清晰定义的接口(如基于PCIe的特定数据包格式)进行通信,确保数据高效、无误地传输。

- 联合调试:开发过程中需使用逻辑分析仪、示波器等工具进行硬件调试,同时结合软件日志进行联合调试,确保从物理层到应用层的全链路功能正确。

###

CPRI协议分析仪的开发是一个复杂的系统工程,涵盖了从高速数字电路设计、FPGA编程到上层应用软件开发的完整链条。硬件设计追求极致的性能与稳定性,软件实现则聚焦于功能的完整性、易用性与智能化。两者相辅相成,共同构成了这款能够洞察移动通信基站内部数据流动的精密测试仪器,为5G及未来移动通信技术的研发与部署提供了至关重要的支撑工具。

如若转载,请注明出处:http://www.didihaohuo.com/product/35.html

更新时间:2026-01-13 12:57:25